# **SVM2608**

# 4-Channel, 100 kSamples/s Analog-to-Digital Converter

**USER'S MANUAL**

P/N: 82-0066-000 Released February 23, 2007

VXI Technology, Inc.

2031 Main Street Irvine, CA 92614-6509 (949) 955-1894

# TABLE OF CONTENTS

| INTRODUCTION                                      |        |

|---------------------------------------------------|--------|

| TABLE OF CONTENTS                                 |        |

| Certification                                     |        |

| Warranty                                          |        |

| Limitation of Warranty                            |        |

| Restricted Rights Legend                          |        |

| DECLARATION OF CONFORMITY                         |        |

| GENERAL SAFETY INSTRUCTIONS                       |        |

| Terms and Symbols                                 |        |

| Warnings                                          |        |

| SUPPORT RESOURCES                                 |        |

| SECTION 1                                         |        |

| Introduction                                      | 1      |

| Introduction                                      |        |

| Overview                                          |        |

| Acquiring Data                                    |        |

| Triggering                                        |        |

| Linear Mode                                       |        |

| Pre-Trigger                                       |        |

| Delayed Trigger                                   |        |

| FIFO Mode                                         |        |

| Calibrations                                      |        |

| Test Bus                                          |        |

| Commands                                          |        |

| Option -01                                        |        |

| Physical Description                              |        |

| Front Panel Interface Wiring                      |        |

| SVM2608 Specifications                            |        |

| •                                                 |        |

| SECTION 2                                         |        |

| Preparation for Use                               |        |

| Introduction                                      |        |

| Calculating System Power and Cooling Requirements |        |

| Setting the Chassis Backplane Jumpers             |        |

| Setting the Base Address                          | 24     |

| Example 1                                         | 2      |

| Example 2                                         | 20     |

| Module Installation/Removal                       | 20     |

| SECTION 3                                         | 2      |

| Programming                                       | 2′     |

| Introduction                                      | 2      |

| Device Memory Maps                                | 2′     |

| Function Offset                                   | 2      |

| Register Offset                                   | 2<br>2 |

| Data(Byte) Ordering                               | 30     |

| Determining the Register Address                  |        |

| Accessing the Registers                           |        |

| Description of Registers                          |        |

| Microprocessor Commands                           |        |

|                                                   |        |

| Measurement Commands                                                       | 41 |

|----------------------------------------------------------------------------|----|

| Captured Data Calculations                                                 | 42 |

| Resistance Measurement – Offset Method                                     | 43 |

| Resistance Measurement – Dynamic Method                                    | 43 |

| Self Test Command                                                          |    |

| Preset Setting Measurement Commands                                        | 44 |

| Calibration Commands                                                       | 45 |

| Error Processing                                                           | 47 |

| Diagnostic Commands                                                        |    |

| Examples                                                                   | 51 |

| Example 1: Setting the Channel 2 and 4 Sample Rate to 123 ms (8.13 kHz)    |    |

| Example 2: Setting Channel 2 to Acquire 200,000 Samples                    | 51 |

| Example 3: Setting Channel 2 to Pre-acquire 100,000 Samples                | 52 |

| Example 4: Setting Channel 2 to Delay Acquisition by 1,500,000 Samples     | 52 |

| Example 5: Setting Channel 2 and 4 Timeout Register to Timeout after 2.5 s | 53 |

| APPENDIX A                                                                 | 55 |

| APPENDIX A                                                                 | 55 |

| Data Swapping Example                                                      | 55 |

| INDEX                                                                      | 57 |

| ±± ₹±≠ ±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±                                    | 7  |

### **CERTIFICATION**

VXI Technology, Inc. (VTI) certifies that this product met its published specifications at the time of shipment from the factory. VTI further certifies that its calibration measurements are traceable to the United States National Institute of Standards and Technology (formerly National Bureau of Standards), to the extent allowed by that organization's calibration facility, and to the calibration facilities of other International Standards Organization members.

### WARRANTY

The product referred to herein is warranted against defects in material and workmanship for a period of one year from the receipt date of the product at customer's facility. The sole and exclusive remedy for breach of any warranty concerning these goods shall be repair or replacement of defective parts, or a refund of the purchase price, to be determined at the option of VTI.

For warranty service or repair, this product must be returned to a VXI Technology authorized service center. The product shall be shipped prepaid to VTI and VTI shall prepay all returns of the product to the buyer. However, the buyer shall pay all shipping charges, duties, and taxes for products returned to VTI from another country.

VTI warrants that its software and firmware designated by VTI for use with a product will execute its programming when properly installed on that product. VTI does not however warrant that the operation of the product, or software, or firmware will be uninterrupted or error free.

### LIMITATION OF WARRANTY

The warranty shall not apply to defects resulting from improper or inadequate maintenance by the buyer, buyer-supplied products or interfacing, unauthorized modification or misuse, operation outside the environmental specifications for the product, or improper site preparation or maintenance.

VXI Technology, Inc. shall not be liable for injury to property other than the goods themselves. Other than the limited warranty stated above, VXI Technology, Inc. makes no other warranties, express or implied, with respect to the quality of product beyond the description of the goods on the face of the contract. VTI specifically disclaims the implied warranties of merchantability and fitness for a particular purpose.

### RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subdivision (b)(3)(ii) of the Rights in Technical Data and Computer Software clause in DFARS 252.227-7013.

VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509 U.S.A.

## DECLARATION OF CONFORMITY

Declaration of Conformity According to ISO/IEC Guide 22 and EN 45014

MANUFACTURER'S NAME VXI Technology, Inc.

MANUFACTURER'S ADDRESS 2031 Main Street

Irvine, California 92614-6509-6509

PRODUCT NAME 4-Channel, 100 kSamples/s Analog-to-Digital Converter

MODEL NUMBER(S) SVM2608

PRODUCT OPTIONS All

PRODUCT CONFIGURATIONS All

VXI Technology, Inc. declares that the aforementioned product conforms to the requirements of the Low Voltage Directive 73/23/EEC and the EMC Directive 89/366/EEC (inclusive 93/68/EEC) and carries the "CE" mark accordingly. The product has been designed and manufactured according to the following specifications:

**SAFETY** EN61010 (2001)

EMC EN61326 (1997 w/A1:98) Class A

CISPR 22 (1997) Class A VCCI (April 2000) Class A

ICES-003 Class A (ANSI C63.4 1992) AS/NZS 3548 (w/A1 & A2:97) Class A

FCC Part 15 Subpart B Class A

EN 61010-1:2001

The product was installed into a C-size VXI mainframe chassis and tested in a typical configuration.

I hereby declare that the aforementioned product has been designed to be in compliance with the relevant sections of the specifications listed above as well as complying with all essential requirements of the Low Voltage Directive.

February 2007

Steve Mauga, QA Manager

# **GENERAL SAFETY INSTRUCTIONS**

Review the following safety precautions to avoid bodily injury and/or damage to the product. These precautions must be observed during all phases of operation or service of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual, violates safety standards of design, manufacture and intended use of the product.

Service should only be performed by qualified personnel.

### TERMS AND SYMBOLS

These terms may appear in this manual:

**WARNING** Indicates that a procedure or condition may cause bodily injury or death.

**CAUTION** Indicates that a procedure or condition could possibly cause damage to

equipment or loss of data.

These symbols may appear on the product:

ATTENTION - Important safety instructions

Frame or chassis ground

Indicates that the product was manufactured after August 13, 2005. This mark is placed in accordance with EN 50419, Marking of electrical and electronic equipment in accordance with Article 11(2) of Directive 2002/96/EC (WEEE). End-of-life product can be returned to VTI by obtaining an RMA number. Fees for take-back and recycling will apply if not prohibited by national law.

### WARNINGS

Follow these precautions to avoid injury or damage to the product:

**Use Proper Power Cord**To avoid hazard, only use the power cord specified for this

product.

Use Proper Power Source To avoid electrical overload, electric shock or fire hazard, do

not use a power source that applies other than the specified

voltage.

**Use Proper Fuse**To avoid fire hazard, only use the type and rating fuse

specified for this product.

### WARNINGS (CONT.)

### **Avoid Electric Shock**

To avoid electric shock or fire hazard, do not operate this product with the covers removed. Do not connect or disconnect any cable, probes, test leads, etc. while they are connected to a voltage source. Remove all power and unplug unit before performing any service. Service should only be performed by qualified personnel.

### **Ground the Product**

This product is grounded through the grounding conductor of the power cord. To avoid electric shock, the grounding conductor must be connected to earth ground.

### **Operating Conditions**

To avoid injury, electric shock or fire hazard:

- Do not operate in wet or damp conditions.

- Do not operate in an explosive atmosphere.

- Operate or store only in specified temperature range.

- Provide proper clearance for product ventilation to prevent overheating.

- DO NOT operate if any damage to this product is suspected.

Product should be inspected or serviced only by qualified personnel.

### **Improper Use**

The operator of this instrument is advised that if the equipment is used in a manner not specified in this manual, the protection provided by the equipment may be impaired. Conformity is checked by inspection.

# **SUPPORT RESOURCES**

Support resources for this product are available on the Internet and at VXI Technology customer support centers.

### VXI Technology World Headquarters

VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509

Phone: (949) 955-1894 Fax: (949) 955-3041

### VXI Technology Cleveland Instrument Division

5425 Warner Road Suite 13 Valley View, OH 44125

Phone: (216) 447-8950 Fax: (216) 447-8951

### VXI Technology Lake Stevens Instrument Division

VXI Technology, Inc. 1924 - 203 Bickford Snohomish, WA 98290

Phone: (425) 212-2285 Fax: (425) 212-2289

### **Technical Support**

Phone: (949) 955-1894 Fax: (949) 955-3041

E-mail: support@vxitech.com

Visit http://www.vxitech.com for worldwide support sites and service plan information.

VXI Technology, Inc.

# SECTION 1

# **INTRODUCTION**

### Introduction

The SVM Series leverages off VXI Technology's line of high-density modular VXIbus instruments, but are optimized for the VMEbus. All SVM instruments are designed to provide all the features of test instrumentation in other platforms such as GPIB or VXI. These features are achieved in hardware rather than in a driver. This approach to the interface design guarantees the user that all communications to the module occur in microseconds, as opposed to several milliseconds, considerably improving system throughput. The board is equipped with a microprocessor which significantly increases the module's functionality and task performing capabilities.

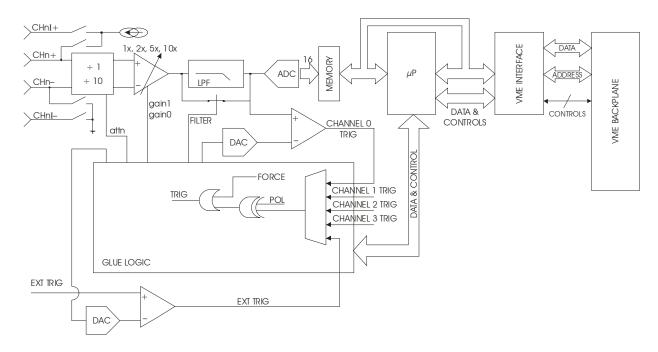

The SVM2608 is a ruggedized circuit card designed for insertion into a convection-cooled VME chassis. It is a double height VME size module (6U) of single slot width and conforms to all physical requirements as specified by VME specifications. The VME interface is compatible with the VME32/64x configuration with two 160-pin (32 x 5) backplane connectors (P0 – P1). The SVM2608 consists of four low-speed (100 kSamples/s) channels and, with the addition of the -01 Option, can include two, high-speed (20 MHz) channels.

### **OVERVIEW**

The SVM2608 is a precision, four channel digitizer capable of capturing data on all four channels simultaneously either in FIFO (or "real-time") mode or Linear (or "burst") mode. A processor enables the user to perform a variety of calculations with the data acquired. Each channel is also capable of measuring voltage and resistance. All four channels can measure voltage at the same time, but resistance can only be measured one channel at a time. Resistance can be measured in two different modes: 2-wire or 4-wire. Both modes use a local current source to inject a current into the resistor under test and then measure voltage across the resistor.

All four channels are independent of one another. The front end of each channel has both a variable gain amplifier and an attenuator, thus allowing for full ADC scale measurements of signals from 1 V to 100 V. Before being digitized, the signal can be passed through a Low Pass Filter (LFP) with a cut-off frequency of 20 kHz. The ADC is a 16-bit converter capable of taking as many as 100 kSamples/s on a scale of -10 V to +10 V. To compensate for offset and gain variation in the ADCs, each channel has two 12-bit DACs that are used to calibrate the offset and the gain on each channel ADC. These calibrations are performed at the factory using precision voltage reference sources.

FIGURE 1-1: SVM2608 BLOCK DIAGRAM

The acquisition process is controlled by two FPGAs that allow for greater flexibility along with higher speed and precision during the digitizing process. As the data is digitized, it is placed in memory. It is then available to the user through the VME interface. Each channel has its own channel memory that can store up to one million samples of data. This data is also made available to the microprocessor for data processing. The samples are stored as words (16 bits). The first sample of a channel is located at the channel's base address at Offset 0 (0x000000 for Channel 0, 0x200000 for Channel 1, 0x400000 for Channel 2 and 0x600000 for Channel 3). The next sample is located at Offset 2 (0x000002 for Channel 0, etc.) and the third sample is located at Offset 4, etc.

In order to provide better resolution for the measurement, the input signal is amplified accordingly to generate a  $\pm 10~V_{P-P}$  signal at the input of the ADC. Thus, on different scales, the weight of a bit of digitized data will be different:

| SCALE (V) | Bit Weight (µV/count) |

|-----------|-----------------------|

| 1         | 30.518                |

| 2         | 61.035                |

| 5         | 152.588               |

| 10        | 305.176               |

| 20        | 610.352               |

| 50        | 1525.879              |

The following equation is used to determine the bit weight at a specified scale:

Bit Weight = Full Scale / 32,768

For example, the Bit Weight of the 10 V range is:

10.0 volts / 32768 = 0.0003051757813 V/count  $\approx 305.176 \,\mu\text{V/count}$

The counts stored in memory are 16 bits **SIGNED** integers. The most significant bit represents the SIGN. Thus, the hex number 0x4000 and the hex number of 0xC000 represent the same signal amplitude but in opposite directions, where 0x4000 represents a positive signal while 0xC000 is a negative signal with the same amplitude.

To translate a raw count value into a voltage, multiply the raw count value by the bit weight. The following example shows this conversion for a SVM2608 using the 10.0 V range:

```

A reading of 0x4000 = 16,384 counts

Voltage = Counts * Bit Weight

Voltage = 16384 counts * 305.176 \muV/count

\approx 5.0 volts.

A reading of 0xC000 = -16,384 counts

Voltage = -16384 counts * 305.176 \muV/count

\approx -5.0 volts.

```

Similarly, for the 5 volt range:

```

A reading of 0x4000 = 16,384 counts

Voltage = 16,384 counts * 152.588 \muV/count

\approx 2.5 volts.

```

Data acquisition can be made in two modes: *Linear* or *FIFO*. In *FIFO* mode, data can only be read from a fixed address (FIFO register), while in *Linear* mode, data can be read from any address in the memory space of a channel. Linear mode also offers a two more options for acquisition: *Pre-Trigger* and *Delayed Trigger*.

In FIFO mode, data can be retrieved while the acquisition is still in progress. However, if the memory is not read and the acquisition continues running, new incoming data will overwrite older data and the older data will be lost. It is also NOT possible to run a measurement command in FIFO mode.

### Acquiring Data

To acquire data, a channel must first be Armed. When a channel is armed, it starts its local Sample Clock and waits for a Trigger Event to begin sampling. The channel must remain Armed for the entire duration of the acquisition process. Clearing the ARM bit will reset the internal state-machines and stop acquisition. Data capturing starts when a Trigger Event occurs. A trigger event can be caused by an external trigger source, the signal under test or forced by setting a bit in a register.

### Triggering

An external signal, other than one of the sampled signals, can be used to trigger any or all of the channels. This external signal is compared to a threshold level set by a local DAC and a high-speed comparator is used to generate an External Trigger signal.

The signal under test can also be used to trigger an acquisition. The signal is compared to a threshold level set by a local DAC and a high-speed comparator is used to generate a Channel Trigger signal. Each channel has its own DAC and its own comparator, thus, each channel can generate a Trigger signal independent of the other channels. Acquisition on any channel can be triggered by any other Channel Trigger signal (Channel 0 can be triggered by *Channel 0 Trigger*, *Channel 1 Trigger*, *Channel 2 Trigger*, or *Channel 3 Trigger*) even if the other channels are not armed and are not acquiring any data. Only one channel can be the trigger source at any time and the trigger sources cannot be AND'ed or OR'ed together.

In absence of a Trigger signal, the acquisition can be forced by setting a control bit, the FORCE bit. Forcing an acquisition on a channel only starts acquisition on that channel. Each channel has its own corresponding FORCE bit.

### Linear Mode

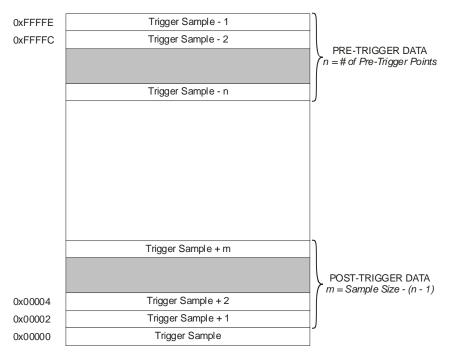

In Linear mode, the total number of samples collected (also referred to as *Sample Points*) is determined by the value programmed into the Sample Points register. The first sample (also referred to as *Sample Zero*) is stored in memory when a Trigger Event occurs. Sample Zero is from the value read from the channel's base address at offset zero (0x000000 for Channel 0, 0x200000 for Channel 1, 0x400000 for Channel 2 and 0x600000 for Channel 3).

### Pre-Trigger

In Linear mode, it is also possible to store samples that occur before a Trigger Event. When a channel is armed and the Pre-Trigger register is programmed with a value other than zero, that channel will begin sampling immediately, without waiting for an External Trigger. After it stores the number of samples specified in the Pre-Trigger register (also referred to as *Pre-Trigger Points*), it begins monitoring the Trigger Event. Until the Trigger Event occurs, the channel continues sampling and storing. When the Trigger Event occurs, Sample Zero is stored. After the Trigger Event, the number of data points collected is determined by the following equation:

### AFTER TRIGGER POINTS = SAMPLE POINTS - PRETRIGGER POINTS

When the user reads from offset zero of a channel, the data returned is Sample Zero followed by Sample Zero + 1, etc. The Pre-Trigger Points can be read from the top of that channel's memory. For example, if 0x100 Pre-Trigger Points were sampled on Channel 0 after the acquisition is completed, the samples can be retrieved from locations 0x1FFE00, 0x1FFE02 ...0x1FFFFE with the data at 0x1FFFFE being the last Pre-Trigger Sample before the trigger event.

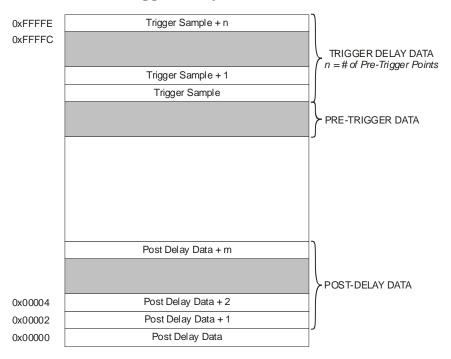

### **Delayed Trigger**

In Linear mode, it is also possible to delay storing Sample Zero by a number of sample clocks, where a sample clock is defined by the Sample Clock Rate register. The number of sample clocks an acquisition is delayed (also referred to as *Delayed Points*) is programmed in the Delayed Trigger register. Samples are taken and stored immediately when the Trigger Event occurs, but Sample Zero will be stored only after the specified number of Delayed Points passes. Data stored during the Delayed period can be viewed by the user at the top of the memory space of the respective channel (same as in Pre-Trigger mode as above), assuming that the following condition is observed:

SAMPLE POINTS < 1 MSamples

As opposed to the Pre-Trigger acquisition, the number of samples taken *after* the Trigger Event is not affected by the number of samples taken *before* it:

AFTER TRIGGER POINTS = SAMPLE POINTS

If the following condition is met:

DELAYED POINTS < 1 M - SAMPLE POINTS

Then all the samples collected before the Trigger Event are available to the user.

### FIFO Mode

In FIFO mode, the user can retrieve data from the board as acquisition progresses. The memory behaves as a FIFO: data is written into a circular buffer with new data overwriting older data when the buffer is full. A Threshold Flag is available to monitor the status of the buffer and prevent overwriting the data or under-reading it.

The Sample Points register that is used in Linear mode to determine the amount of data to be captured is used in FIFO mode to determine the size associated with the FIFO Threshold Flag. When the number of samples stored in memory equals the number of points set in the Sample Points register, the FIFO Threshold flag is asserted. In this manner, the user can wait until a certain number of samples are captured before they download data from the board. If the user fails to retrieve the data from the card in time and new data overwrites older data, then the FIFO Overrun flag is asserted. Conversely, if the user attempts to read more data than has been stored, the FIFO Underrun flag is asserted. The FIFO Threshold flag is cleared when data is read from the board and the total amount of "new (unread)" data in the buffer is less than the THRESHOLD value. The FIFO Overrun and Underrun flags are cleared only when a new acquisition is initiated.

### **Calibrations**

Due to the nature of the semiconductors and passive components, not all parts have exactly the same characteristics. Slight differences exist from component to component. While these inconsistencies are unavoidable, they do not affect the basic functionality of the electronic instrumentation. The precision of the instrument, however, can be altered by these variances.

One way to eliminate these slight variations is to use expensive, precision parts or to perform a rigorous parts selection procedure to ensure consistency. These measures, however, would dramatically increase the cost of the board. Another way to compensate for offset and gain variations is to take a number of measurements using precision calibrated instruments of known voltage and resistance. Their known values are then compared against the values attained for each channel and the difference is used to adjust future measurements. These adjustments are called *calibrations*. They are performed at the factory using approved calibration sources.

### Test Bus

The SVM2608 is capable of performing a self-test to check for functionality and accuracy. Using a local voltage reference source and local resistance references, basic function tests can be performed. Four different voltage reference sources are available on the board:  $\pm 9.45$  V and  $\pm 0.945$  V. Two Resistance References are available:  $128 \Omega$  and  $81.92 \text{ k}\Omega$ . Two different signal generators can also be used for different tests: a RAMP generator and a PULSE generator. Any of these locally generated test sources can be placed on the internal Test Bus (TB). The Test Bus can then be connected to the input of any or all of the channels. Only one of the test signals can be connected to the Test Bus at one time. The test sources can be connected to the Test Bus using microprocessor commands. The Test Bus is also available to the user for monitoring on pins 24 and 13 of the Front Panel Connector. (See *Front Panel Interface Wiring* for more detail.)

The self-test is performed by sending a command to the microprocessor, instructing it to run the self-test (see *Microprocessor Commands*). When the microprocessor runs the self-test, a Test Result is returned (see the description of the Self Test Command for a more detailed description).

### **Commands**

The SVM2608 is equipped with a processor. While the processor is not directly involved in the acquisition process, its presence on the board significantly enhances the capabilities of the SVM2608 digitizer.

The user can choose to download the data on to a CPU and perform custom data processing, or they can instruct the on-board microprocessor to perform one or several predefined calculations

sets. (See *Microprocessor Commands* for more details on available commands.) The command is sent to the microprocessor via the Command register. Since there are four independent channels on the board, each of them can take a different command and each of them has its own command register. The result of the microprocessor calculation is returned in the Result register for the corresponding channel.

The data stored in the channel memory is *raw* data. When the microprocessor performs a resistance calculation, it uses *calibrated* data, meaning that the microprocessor takes the calibrations for the Local Current Sources (see above) values into consideration. The raw data the user downloads from the board represents calibrated voltage measurements. The result calculated by the microprocessor and placed in the Result register when a Resistance Measurement command is issued is based on calibrated Current measurements. While the user can perform calibrated *voltage* measurements by simply reading the raw data, the calculations for *resistance* cannot be accurately performed by the user as they do not have the calibrated *current* values (the exact values injected in the resistance under test by the board's current source). Although it is possible for the user to read the calibration values (see the *Calibration Commands* section) and use the raw data to perform all the calibrated measurements on their own, the manufacturer encourages the use of the microprocessor's capabilities to perform all calibrated resistance calculations.

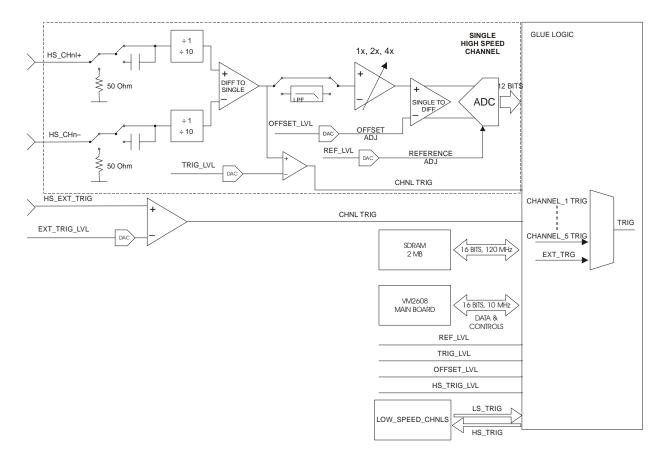

### Option -01

With the addition of the SVM2608-01 option, two additional channels are available with a sample rate of 20 MHz and 12-bits of resolution. This option may be purchased at the same time as the SVM2608 or is factory upgradeable.

The high-speed channels available on Option -01 function independently. The front end of each channel has both a variable gain amplifier and an attenuator, similar to the low-speed channels. A 5 MHz low-pass filter (LPF) is available on these channels, as opposed to the 20 kHz LPF found on the low-speed channels. The ADC converter is a 12 bits converter capable of taking as many as 20 MSamples/s on a scale of -2 V to +2 V. To compensate for offset and gain variation in the ADCs, each channel has two 12 bits DACs that are used to calibrate the offset and the gain on each ADC channel. These calibrations are performed at the factory using precision voltage reference sources. A block diagram for Option -01 is provided on the following page.

FIGURE 1-2: SVM2608 BLOCK DIAGRAM

# O O A/E P/F

### PHYSICAL DESCRIPTION

The SVM2608 has a protective coating applied to it to ensure that the effects of environmental hazards are minimized. This coating endows the modules with resistance to salt sprays, moisture, dust, sand, and explosive environments, as the polymer coating provides a hermetic seal. The module is designed to withstand the stress and rigors of shock and vibration, allowing the module to be deployed in a variety of applications without concern for damage due to the surrounding physical environment. The following table details the environmental specifications of this module.

TABLE 1-1: SVM2608 ENVIRONMENTAL SPECIFICATIONS

| SVM ENVIRONMENTAL SE | SVM Environmental Specifications                                                        |  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| CLASSIFICATION       | MIL-T-28800E Type III, Class 5, Style E or F                                            |  |  |  |  |

| TEMPERATURE          | Meets functional shock requirements of MIL-T-28800E, Type III, Class 5                  |  |  |  |  |

| OPERATIONAL          | -20°C to 65°C                                                                           |  |  |  |  |

| NON-OPERATIONAL      | -40°C to 71°C                                                                           |  |  |  |  |

| HUMIDITY             | 5% to 95% (non-condensing)                                                              |  |  |  |  |

| ALTITUDE             |                                                                                         |  |  |  |  |

| OPERATIONAL          | Sea level to 15,000 ft (4,570 m)                                                        |  |  |  |  |

| SUSTAINED STORAGE    | Sea level to 40,000 ft (12,190 m)                                                       |  |  |  |  |

| RANDOM VIBRATION     | Three axis, 30 minutes total, 10 minutes per axis                                       |  |  |  |  |

| <b>OPERATIONAL</b>   | $0.27  g_{rms}$ total from $5.0  Hz$ to $55.0  Hz$                                      |  |  |  |  |

| NON-OPERATIONAL      | 2.28 g <sub>rms</sub> total from 5.0 Hz to 55.0 Hz                                      |  |  |  |  |

| FUNCTIONAL SHOCK     | Half sine, 30 g, 11 ms duration                                                         |  |  |  |  |

| SALT ATMOSPHERE      | > 48 hrs operation                                                                      |  |  |  |  |

| SAND AND DUST        | > 6 hrs operation in a dust environment of 0.3 g/ft <sup>3</sup> blowing at 1750 ft/min |  |  |  |  |

The SVM2608 has two indicator LEDs located on its front panel. The A/E (Access/Error) LED flashes green when read/write commands are being sent to the module. Should the SVM2608 receive an error, the LED glows red. This LED can be overridden by the user by setting the Sysfail bit in the *Reset, Sys Fail Control, Interrupt Levels Register*. The P/F (Power/Fail) LED glows green indicates the status of a processor driven self-test. If the self-test is successful, the P/F LED glows green, if the test fails, however, the LED will glow red. Both the A/E and P/F LEDs can be programmed to glow red when a fail condition occurs.

FIGURE 1-3: SVM2608 FRONT PANEL

Note

### FRONT PANEL INTERFACE WIRING

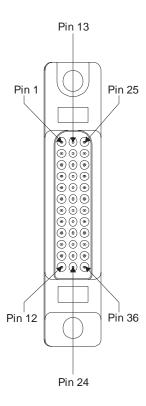

Front-panel connector, J101, contains all the instrument signals for the Channels 0 through 3.

| PIN NUMBER | SIGNAL | PIN NUMBER | SIGNAL    | PIN NUMBER | SIGNAL |

|------------|--------|------------|-----------|------------|--------|

| 1          | GND    | 13         | TB-       | 25         | GND    |

| 2          | CH1I-  | 14         | GND       | 26         | CH3I-  |

| 3          | CH1-   | 15         | GND       | 27         | CH3-   |

| 4          | CH1+   | 16         | GND       | 28         | CH3+   |

| 5          | CH1I+  | 17         | GND       | 29         | CH3I+  |

| 6          | GND    | 18         | GND       | 30         | GND    |

| 7          | GND    | 19         | EXTTRIGIN | 31         | GND    |

| 8          | CH0I-  | 20         | GND       | 32         | CH2I-  |

| 9          | CH0-   | 21         | GND       | 33         | CH2-   |

| 10         | CH0+   | 22         | GND       | 34         | CH2+   |

| 11         | CH0I+  | 23         | GND       | 35         | CH2I+  |

| 12         | GND    | 24         | TB+       | 36         | GND    |

FIGURE 1-4: SVM2608 PIN LOCATIONS

The SMA connectors associated with the high-speed channels are labeled on the front panel and are capable of being triggered by a different external trigger source than the low-speed channels.

### **SVM2608 SPECIFICATIONS**

| GENERAL SPECIFICATIONS         |                                                                                    |

|--------------------------------|------------------------------------------------------------------------------------|

| Number of Channels             |                                                                                    |

| TOMBER OF CHARLES              | 4                                                                                  |

| SAMPLING RATE                  |                                                                                    |

| Range                          | 0.59 Samples/s to 100.0 kSamples/s                                                 |

| Resolution                     | 100 ns                                                                             |

| Accuracy                       | 1%                                                                                 |

| INPUT POWER                    | 170                                                                                |

| +5 V dc                        | 500 mA                                                                             |

| +3 V dc<br>+12 V dc            | 300 mA                                                                             |

| -12 V dc                       | 300 mA                                                                             |

| VMEBUS INTERFACE               | 300 IIIA                                                                           |

|                                | A 22                                                                               |

| Address mode                   | A32<br>D16 or D32                                                                  |

| Data transfer mode             | D10 0f D32                                                                         |

| MEMORY                         | 11/0 1 1 1                                                                         |

|                                | 1 MSamples per channel                                                             |

| VOLTAGE MEASUREMENT            |                                                                                    |

| Range                          | ±1.0 V, ±2.0 V, ±5.0 V, ±10.0 V, ±20.0 V, ±50.0 V                                  |

| Resolution                     | 1/2 <sup>15</sup> of full scale                                                    |

| Accuracy                       | 1%                                                                                 |

| INPUT IMPEDANCE                |                                                                                    |

| 20 & 50 V Range                | 200 kΩ                                                                             |

| 1, 2, 5 & 10 V Range           | $> 10 \text{ M}\Omega$                                                             |

| RESISTANCE MEASUREMENT*        |                                                                                    |

| Range                          | $100 \Omega$ , 1 kΩ, $10 k\Omega$ , $100 k\Omega$ , 1 MΩ, $100\%$ over range*      |

| Resolution                     | 1/6,553.6 of scale                                                                 |

| Accuracy                       | 1%                                                                                 |

| *Note: Resistance measurement. | s can only be made one channel at a time.                                          |

| All resistance measureme       | ents can be made accurately up to $+199\%$ of the set range.                       |

| INPUT FILTER                   | , , , , , , , , , , , , , , , , , , , ,                                            |

|                                | 20 kHz (-3 dB)                                                                     |

| TRIGGER LEVELS                 | 20 KIE ( 3 GB)                                                                     |

| Internal                       |                                                                                    |

| Range                          | trigger level determined by selected voltage range (see Voltage Measurement above) |

| Trigger level resolution       | Range/2 <sup>11</sup>                                                              |

| Level accuracy                 | 1%                                                                                 |

| External                       | I/V                                                                                |

| Range                          | -10 V to +10 V                                                                     |

| Trigger level resolution       | 4.88 mV                                                                            |

| Level accuracy                 | 1%                                                                                 |

| DELAYED TRIGGER                |                                                                                    |

| Range                          | 0 samples to (2 <sup>32</sup> -1) samples                                          |

| Resolution                     | 1 sample                                                                           |

| TIMEOUT                        |                                                                                    |

| Range                          | 10 μs to 227 hrs                                                                   |

| Resolution                     | 10 μs to 100 s                                                                     |

| WARM-UP TIME                   | - v Lux . v - v v v                                                                |

| WARM-ULTIME                    | 10 min                                                                             |

| MTBF                           | 1V IIIII                                                                           |

| IVIIDF                         | 80,000 hrs (based on 20% Ground Mobile, 80% Ground Fixed environment, T ≥ 52°C)    |

|                                |                                                                                    |

| OPTION 1 - SVM2608-01                 |                                                                                           |

|---------------------------------------|-------------------------------------------------------------------------------------------|

| Number of Channels                    |                                                                                           |

| NUMBER OF CHANNELS                    | 2                                                                                         |

| VMEBUS INTERFACE                      |                                                                                           |

| Address Mode                          | A32                                                                                       |

| Address Mode Data Transfer Mode       | D16 or D32                                                                                |

|                                       | D10 01 D32                                                                                |

| SAMPLING RATE                         |                                                                                           |

| Range                                 | 7.15 Samples/s to 20.0 MSamples/s                                                         |

| Resolution                            | 8.333 ns                                                                                  |

| Accuracy                              | 1%                                                                                        |

| MEMORY                                |                                                                                           |

| <u>,</u>                              | 1 MSamples per channel                                                                    |

| VOLTAGE MEASUREMENTS                  |                                                                                           |

| Range                                 | ±0.5 V, ±1.0 V, ±2.0 V, ±5.0 V, ±10.0 V, ±20.0 V                                          |

| Resolution                            | Range/2 <sup>11</sup>                                                                     |

| Accuracy                              | 1%                                                                                        |

| INPUT IMPEDANCE                       |                                                                                           |

|                                       | 1 M $\Omega$ or 50 $\Omega$ (software selectable)                                         |

| INPUT MODE                            |                                                                                           |

|                                       | ac or dc (software selectable)                                                            |

| INPUT FILTER                          | w or w (oorman borownor)                                                                  |

| INTOTTIETER                           | 5 MHz (-3 dB)                                                                             |

| TRIGGER LEVELS                        | JANIE (Jub)                                                                               |

| Internal                              |                                                                                           |

| Range                                 | trigger level determined by selected voltage range (see <i>Voltage Measurement</i> above) |

| Trigger level resolution              | Full scale/2 <sup>11</sup>                                                                |

| Level accuracy                        | 1%                                                                                        |

| External                              | 1/0                                                                                       |

| Range                                 | -10 V to +10 V                                                                            |

| Trigger level resolution              | 4.88 mV                                                                                   |

| Level accuracy                        | 1%                                                                                        |

| DELAYED TRIGGER                       |                                                                                           |

| Range                                 | 0 samples to (2 <sup>24</sup> -1) samples                                                 |

| Resolution                            | 1 sample                                                                                  |

| TRIGGER ACCURACY                      | 1 omitper                                                                                 |

| I MIGGEN ACCUNACT                     |                                                                                           |

|                                       | 10/2                                                                                      |

| EVTERNAL TRICGER ACCUM                | 1%                                                                                        |

| EXTERNAL TRIGGER ACCUR                | RACY                                                                                      |

|                                       |                                                                                           |

| TIMEOUT                               | RACY<br>1%                                                                                |

| TIMEOUT<br>Range                      | 1% 10 μs to 227 hrs                                                                       |

| TIMEOUT Range Resolution              | RACY<br>1%                                                                                |

| TIMEOUT<br>Range                      | 1%  10 μs to 227 hrs 10 μs to 100 s                                                       |

| TIMEOUT Range Resolution WARM-UP TIME | 1% 10 μs to 227 hrs                                                                       |

| TIMEOUT Range Resolution              | 1%  10 μs to 227 hrs 10 μs to 100 s                                                       |

VXI Technology, Inc.

# **SECTION 2**

# PREPARATION FOR USE

### Introduction

When the SVM2608 is unpacked from its shipping carton, the contents should include the following items:

- (1) SVM2608 4 Channel 100 kSamples/s Analog-to-Digital Converter Module

- (1) SVM2608 User's Manual (this manual)

All components should be immediately inspected for damage upon receipt of the unit. Installation instructions for the module are discussed in the following pages of this section.

The chassis the SVM2608 is installed in should be checked to ensure that it is capable of providing adequate power and cooling. Once it is found that the chassis meets these specifications, the SVM2608 should be examined. If the module is found to be in good condition, the base address of the SVM2608 and the backplane jumpers of the chassis may be configured. After setting the base address and chassis jumpers, the SVM2608 may be installed into an appropriate 6U VMEbus mainframe in any slot other than slot zero.

### CALCULATING SYSTEM POWER AND COOLING REQUIREMENTS

It is imperative that the chassis provide adequate power and cooling for this module. Referring to the chassis operation manual, confirm that the power budget for the system (the chassis and all modules installed therein) is not exceeded and that the cooling system can provide adequate cooling.

It should be noted that if the chassis cannot provide adequate power to the module, the instrument might not perform to specification or possibly not operate at all. In addition, if adequate cooling is not provided, the reliability of the instrument will be jeopardized and permanent damage may occur. Damage found to have occurred due to inadequate cooling could also void the warranty of the module.

### SETTING THE CHASSIS BACKPLANE JUMPERS

Please refer to the chassis operation manual for further details on setting the backplane jumpers.

### **SETTING THE BASE ADDRESS**

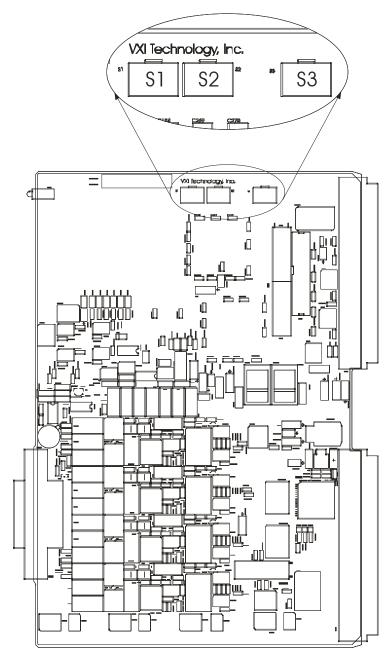

The base address of the SVM2608 is determined by using the offset value (OV), set by two rotary switches located on the top edge of the interface card (Figure 2-1), and multiplying it by  $2^{24}$  (or 16,777,216) to get the base address in A32 address space. The switches are labeled with positions 0 through F. The switch located at S3 corresponds to the Most Significant Bit (MSB) and S2 corresponds to the Least Significant Bit (LSB). (Note, S1 is not used in the determination of the base address.) To set the OV to 25, first convert the decimal number to the hexadecimal value of 0x19. Next, set switch S3 to 1, and then set switch S2 to 9. See Figure 2-2. Two conversion examples are provided on the following pages.

FIGURE 2-1: ROTARY SWITCH LOCATIONS

### Example 1

| OV<br>(decimal) | Divide<br>by 16 |   | MSB  | LSB            |                                                                             |

|-----------------|-----------------|---|------|----------------|-----------------------------------------------------------------------------|

| 25              | 25 / 16         | = | 1    | w/ 9 remaining | Divide the decimal value by 16 to get the MSB and the LSB.                  |

|                 |                 | = | 0001 | 1001           | The 1 is the MSB, and the remainder of 9 is the LSB.                        |

|                 |                 | = | 1    | 9              | Convert to hexadecimal. Set the back switch to 1 and the front switch to 9. |

FIGURE 2-2: OFFSET VALUE EXAMPLE 1

Here is another way of looking at the conversion:

$$OV = (S3 \times 16) + S2$$

$$OV = (1 \times 16) + 9$$

$$OV = 16 + 9$$

OV = 25

The base address is then determined by using the following formula:

A32 Base Address = Offset Value \* 0x1000000 (or 16,777,216)

In this case:

A32 Base Address = 0x19 \* 0x1000000 (or 16,777,216) A32 Base Address = 0x19000000

| OV<br>(decimal) | Divide<br>by 16 |   | MSB  | LSB           |                                                                             |

|-----------------|-----------------|---|------|---------------|-----------------------------------------------------------------------------|

| 200             | 200 / 16        | = | 12   | w/8 remaining | Divide by 16.                                                               |

|                 |                 | = | 1100 | 1000          | Convert to MSB and LSB.                                                     |

|                 |                 | = | C    | 8             | Convert to hexadecimal. Set the back switch to C and the front switch to 8. |

|                 |                 |   | S3   |               | S2                                                                          |

FIGURE 2-3: OFFSET VALUE EXAMPLE 2

Therefore, the base address in this example is:

```

A32 Base Address = 0xC8 * 0x1000000 (or 16,777,216)

A32 Base Address = 0xC8000000

```

This information is used to write to the registers of the SVM2608. (See Section 3 for more details on SVM2608 registers.)

### MODULE INSTALLATION/REMOVAL

Before installing an SVM2608 module into a 6U VME mainframe, make sure that the mainframe is powered down. Insert the module into the base unit by orienting the module so that the flanges at the edge of the module can be inserted into the slot of the base unit. Position the flanges so that they fit into the module slot groove. Once the module is properly aligned, push the module back and firmly insert it into the backplane connector. The retaining screws can then be used to secure the module in the chassis.

To remove the module, power down the mainframe and remove all cabling from the module. The retaining screws can then be loosened. The ejector handles can then be used as to assist in the removal of the module.

# **SECTION 3**

# **PROGRAMMING**

### Introduction

The SVM2608 modules are VMEbus register-based devices for high-speed D16 or D32 data retrieval. Register-based programming is a series of **reads** and **writes** directly to the module registers. This eliminates the time for command parsing thus increasing speed.

### **DEVICE MEMORY MAPS**

### Function Offset

The function offset helps define where in A32 space a WRITE or READ operation is performed. The offsets are defined as follows:

| Function         | Decimal Value | Hexadecimal Value |

|------------------|---------------|-------------------|

| CH0 Data         | 0             | 0x000000          |

| CH1 Data         | 2097152       | 0x200000          |

| CH2 Data         | 4194304       | 0x400000          |

| CH3 Data         | 6291456       | 0x600000          |

| CH4 (Option -01) | 8388608       | 0x800000          |

| CH5 (Option -01) | 10485760      | 0xA00000          |

| Registers        | 12582912      | 0xC00000          |

| Reserved         | 14680064      | 0xE00000          |

CH0 – 5 Data These addresses are used to store data.

**Registers** These addresses are the A32 memory registers. They are used to program the

settings for each channel, collect FIFO data, collect results or sent commands

to the microprocessor.

**Reserved** These addresses are reserved for future use.

### Register Offset

The register offset is located within the module's A32 address space. When data is sent to a register address, the address that is written to is the sum of the module base address, the function offset and the register offset:

Register Address = Module Base Address + Function Offset + Register Offset

Table 3-1 shows the A32 map of the SVM2608 registers.

TABLE 3-1: SVM2608 A32 REGISTER MAP

Note MS = Most Significant LS = Least Significant

| OFFSET | WRITE FUNCTION                        | READ FUNCTION                         |

|--------|---------------------------------------|---------------------------------------|

| 0x00   | Sysfail Control, Interrupt Levels     | Sysfail Control, Interrupt Levels     |

| 0x02   | Force Trigger/Start                   | Force Trigger/Start                   |

| 0x04   | Reserved                              | Reserved                              |

| 0x06   | External Trigger Level                | External Trigger Level                |

| 0x08   | Control (Channel 0)                   | Control (Channel 0)                   |

| 0x0A   | Trigger Level (Channel 0)             | Trigger Level (Channel 0)             |

| 0x0C   | Sample Rate (Channel 0) – (MS)        | Sample Rate (Channel 0) – (MS)        |

| 0x0E   | Sample Rate (Channel 0) – (LS)        | Sample Rate (Channel 0) – (LS)        |

| 0x10   | Sample Points (Channel 0) – (MS)      | Sample Points (Channel 0) – (MS)      |

| 0x12   | Sample Points (Channel 0) – (LS)      | Sample Points (Channel 0) – (LS)      |

| 0x14   | Pre-Trigger Points (Channel 0) – (MS) | Pre-Trigger Points (Channel 0) – (MS) |

| 0x16   | Pre-Trigger Points (Channel 0) – (LS) | Pre-Trigger Points (Channel 0) – (LS) |

| 0x18   | Trigger Delay (Channel 0) – (MS)      | Trigger Delay (Channel 0) – (MS)      |

| 0x1A   | Trigger Delay (Channel 0) – (LS)      | Trigger Delay (Channel 0) – (LS)      |

| 0x1C   | Timeout (Channel 0)                   | Timeout (Channel 0)                   |

| 0x1E   | Interrupt Enable (Channel 0)          | Interrupt Enable (Channel 0)          |

| 0x20   | Reserved                              | Interrupt Status (Channel 0)          |

| 0x22   | Command Register (Channel 0)          | Command Register (Channel 0)          |

| 0x24   | Reserved                              | FIFO Data (Channel 0) – (MS)          |

| 0x26   | Reserved                              | FIFO Data (Channel 0) – (LS)          |

| 0x28   | Reserved                              | Result Register (Channel 0) – (MS)    |

| 0x2A   | Reserved                              | Result Register (Channel 0) – (LS)    |

| 0x2C   | Reserved                              | Result Register (Channel 0) – (MS)    |

| 0x2E   | Reserved                              | Result Register (Channel 0) – (LS)    |

| 0x30   | Control (Channel 1)                   | Control (Channel 1)                   |

| 0x32   | Trigger Level (Channel 1)             | Trigger Level (Channel 1)             |

| 0x34   | Sample Rate (Channel 1) – (MS)        | Sample Rate (Channel 1) – (MS)        |

| 0x36   | Sample Rate (Channel 1) – (LS)        | Sample Rate (Channel 1) – (LS)        |

| 0x38   | Sample Points (Channel 1) – (MS)      | Sample Points (Channel 1) – (MS)      |

| 0x3A   | Sample Points (Channel 1) – (LS)      | Sample Points (Channel 1) – (LS)      |

| 0x3C   | Pre-Trigger Points (Channel 1) – (MS) | Pre-Trigger Points (Channel 1) – (MS) |

| 0x3E   | Pre-Trigger Points (Channel 1) – (LS) | Pre-Trigger Points (Channel 1) – (LS) |

| 0x40   | Trigger Delay (Channel 1) – (MS)      | Trigger Delay (Channel 1) – (MS)      |

| 0x42   | Trigger Delay (Channel 1) – (LS)      | Trigger Delay (Channel 1) – (LS)      |

| 0x44   | Timeout (Channel 1)                   | Timeout (Channel 1)                   |

| 0x46   | Interrupt Enable (Channel 1)          | Interrupt Enable (Channel 1)          |

| 0x48   | Reserved                              | Interrupt Status (Channel 1)          |

| 0x4A   | Command Register (Channel 1)          | Command Register (Channel 1)          |

| 0x4C   | Reserved                              | FIFO Data (Channel 1) – (MS)          |

| 0x4E   | Reserved                              | FIFO Data (Channel 1) – (LS)          |

| 0x50   | Reserved                              | Result Register (Channel 1) – (MS)    |

| 0x52   | Reserved                              | Result Register (Channel 1) – (LS)    |

| 0x54   | Reserved                              | Result Register (Channel 1) – (MS)    |

| OFFSET | WRITE FUNCTION                        | READ FUNCTION                         |  |

|--------|---------------------------------------|---------------------------------------|--|

| 0x56   | Reserved                              | Result Register (Channel 1) – (LS)    |  |

| 0x58   | Control (Channel 2)                   | Control (Channel 2)                   |  |

| 0x5A   | Trigger Level (Channel 2)             | Trigger Level (Channel 2)             |  |

| 0x5C   | Sample Rate (Channel 2) – (MS)        | Sample Rate (Channel 2) – (MS)        |  |

| 0x5E   | Sample Rate (Channel 2) – (LS)        | Sample Rate (Channel 2) – (LS)        |  |

| 0x60   | Sample Points (Channel 2) – (MS)      | Sample Points (Channel 2) – (MS)      |  |

| 0x62   | Sample Points (Channel 2) – (LS)      | Sample Points (Channel 2) – (LS)      |  |

| 0x64   | Pre-Trigger Points (Channel 2) – (MS) | Pre-Trigger Points (Channel 2) – (MS) |  |

| 0x66   | Pre-Trigger Points (Channel 2) – (LS) | Pre-Trigger Points (Channel 2) – (LS) |  |

| 0x68   | Trigger Delay (Channel 2) – (MS)      | Trigger Delay (Channel 2) – (MS)      |  |

| 0x6A   | Trigger Delay (Channel 2) – (LS)      | Trigger Delay (Channel 2) – (LS)      |  |

| 0x6C   | Timeout (Channel 2)                   | Timeout (Channel 2)                   |  |

| 0x6E   | Interrupt Enable (Channel 2)          | Interrupt Enable (Channel 2)          |  |

| 0x70   | Reserved                              | Interrupt Status (Channel 2)          |  |

| 0x72   | Command Register (Channel 2)          | Command Register (Channel 2)          |  |

| 0x74   | Reserved                              | FIFO Data (Channel 2) – (MS)          |  |

| 0x76   | Reserved                              | FIFO Data (Channel 2) – (LS)          |  |

| 0x78   | Reserved                              | Result Register (Channel 2) – (MS)    |  |

| 0x7A   | Reserved                              | Result Register (Channel 2) – (LS)    |  |

| 0x7C   | Reserved                              | Result Register (Channel 2) – (MS)    |  |

| 0x7E   | Reserved                              | Result Register (Channel 2) – (LS)    |  |

| 0x80   | Control (Channel 3)                   | Control (Channel 3)                   |  |

| 0x82   | Trigger Level (Channel 3)             | Trigger Level (Channel 3)             |  |

| 0x84   | Sample Rate (Channel 3) – (MS)        | Sample Rate (Channel 3) – (MS)        |  |

| 0x86   | Sample Rate (Channel 3) – (LS)        | Sample Rate (Channel 3) – (LS)        |  |

| 0x88   | Sample Points (Channel 3) – (MS)      | Sample Points (Channel 3) – (MS)      |  |

| 0x8A   | Sample Points (Channel 3) – (LS)      | Sample Points (Channel 3) – (LS)      |  |

| 0x8C   | Pre-Trigger Points (Channel 3) – (MS) | Pre-Trigger Points (Channel 3) – (MS) |  |

| 0x8E   | Pre-Trigger Points (Channel 3) – (LS) | Pre-Trigger Points (Channel 3) – (LS) |  |

| 0x90   | Trigger Delay (Channel 3) – (MS)      | Trigger Delay (Channel 3) – (MS)      |  |

| 0x92   | Trigger Delay (Channel 3) – (LS)      | Trigger Delay (Channel 3) – (LS)      |  |

| 0x94   | Timeout (Channel 3)                   | Timeout (Channel 3)                   |  |

| 0x96   | Interrupt Enable (Channel 3)          | Interrupt Enable (Channel 3)          |  |

| 0x98   | Reserved                              | Interrupt Status (Channel 3)          |  |

| 0x9A   | Command Register (Channel 3)          | Command Register (Channel 3)          |  |

| 0x9C   | Reserved                              | FIFO Data (Channel 3) – (MS)          |  |

| 0x9E   | Reserved                              | FIFO Data (Channel 3) – (LS)          |  |

| 0xA0   | Reserved                              | Result Register (Channel 3) – (MS)    |  |

| 0xA2   | Reserved                              | Result Register (Channel 3) – (LS)    |  |

| 0xA4   | Reserved                              | Result Register (Channel 3) – (MS)    |  |

| 0xA6   | Reserved                              | Result Register (Channel 3) – (LS)    |  |

| 0xA8   | Control (Channel 4)                   | Control (Channel 4)                   |  |

| 0xAA   | Trigger Level (Channel 4)             | Trigger Level (Channel 4)             |  |

| 0xAC   | Sample Rate (Channel 4) – (MS)        | Sample Rate (Channel 4) – (MS)        |  |

| 0xAE   | Sample Rate (Channel 4) – (LS)        | Sample Rate (Channel 4) – (LS)        |  |

| 0xB0   | Sample Points (Channel 4) – (MS)      | Sample Points (Channel 4) – (MS)      |  |

| 0xB2   | Sample Points (Channel 4) – (LS)      | Sample Points (Channel 4) – (LS)      |  |

| 0xB4   | Pre-Trigger Points (Channel 4) – (MS) | Pre-Trigger Points (Channel 4) – (MS) |  |

| OFFSET | WRITE FUNCTION                                | READ FUNCTION                                 |

|--------|-----------------------------------------------|-----------------------------------------------|

| 0xB6   | Pre-Trigger Points (Channel 4) – (LS)         | Pre-Trigger Points (Channel 4) – (LS)         |

| 0xB8   | Trigger Delay (Channel 4) – (MS)              | Trigger Delay (Channel 4) – (MS)              |

| 0xBA   | Trigger Delay (Channel 4) – (LS)              | Trigger Delay (Channel 4) – (LS)              |

| 0xBC   | Timeout (Channel 4)                           | Timeout (Channel 4)                           |

| 0xBE   | Interrupt Enable (Channel 4)                  | Interrupt Enable (Channel 4)                  |

| 0xC0   | Reserved                                      | Interrupt Status (Channel 4)                  |

| 0xC2   | Command Register (Channel 4)                  | Command Register (Channel 4)                  |

| 0xC4   | Reserved                                      | FIFO Data (Channel 4) – (MS)                  |

| 0xC6   | Reserved                                      | FIFO Data (Channel 4) – (LS)                  |

| 0xC8   | Reserved                                      | Result Register (Channel 4) – (MS)            |

| 0xCA   | Reserved                                      | Result Register (Channel 4) – (LS)            |

| 0xCC   | Reserved                                      | Result Register (Channel 4) – (MS)            |

| 0xCE   | Reserved                                      | Result Register (Channel 4) – (LS)            |

| 0xD0   | Control (Channel 5)                           | Control (Channel 5)                           |

| 0xD2   | Trigger Level (Channel 5)                     | Trigger Level (Channel 5)                     |

| 0xD4   | Sample Rate (Channel 5) – (MS)                | Sample Rate (Channel 5) – (MS)                |

| 0xD6   | Sample Rate (Channel 5) – (LS)                | Sample Rate (Channel 5) – (LS)                |

| 0xD8   | Sample Points (Channel 5) – (MS)              | Sample Points (Channel 5) – (MS)              |

| 0xDA   | Sample Points (Channel 5) – (LS)              | Sample Points (Channel 5) – (LS)              |

| 0xDC   | Pre-Trigger Points (Channel 5) – (MS)         | Pre-Trigger Points (Channel 5) – (MS)         |

| 0xDE   | Pre-Trigger Points (Channel 5) – (LS)         | Pre-Trigger Points (Channel 5) – (LS)         |

| 0xE0   | Trigger Delay (Channel 5) – (MS)              | Trigger Delay (Channel 5) – (MS)              |

| 0xE2   | Trigger Delay (Channel 5) – (LS)              | Trigger Delay (Channel 5) – (LS)              |

| 0xE4   | Timeout (Channel 5)                           | Timeout (Channel 5)                           |

| 0xE6   | Interrupt Enable (Channel 5)                  | Interrupt Enable (Channel 5)                  |

| 0xE8   | Reserved                                      | Interrupt Status (Channel 5)                  |

| 0xEA   | Command Register (Channel 5)                  | Command Register (Channel 5)                  |

| 0xEC   | Reserved                                      | FIFO Data (Channel 5) – (MS)                  |

| 0xEE   | Reserved                                      | FIFO Data (Channel 5) – (LS)                  |

| 0xF0   | Reserved                                      | Result Register (Channel 5) – (MS)            |

| 0xF2   | Reserved                                      | Result Register (Channel 5) – (LS)            |

| 0xF4   | Reserved                                      | Result Register (Channel 5) – (MS)            |

| 0xF6   | Reserved                                      | Result Register (Channel 5) – (LS)            |

| 0xF8   | Reserved                                      | Reserved                                      |

| 0xFA   | Reserved                                      | Reserved                                      |

| 0xFC   | Reserved                                      | Reserved                                      |

| 0xFE   | External Trigger Level for High-Speed Channel | External Trigger Level for High-Speed Channel |

### DATA(BYTE) ORDERING

When a pair of 16-bit registers is read as a 32-bit register, the content of the register marked MS is placed on the VME Bus on D31 - D16 and the content of the register marked LS is placed on D15 - D0. Similarly, when a pair of 16-bit registers is written as a 32-bit register, the register marked MS is loaded with the data present on the VME Bus on D31 - D16 and the register marked LS is loaded with the data present on D15 - D0. All other registers should be addressed as 16-bit registers to prevent any malfunctioning.

With a variety of systems and bridges that move the data between different bus types (i.e. VME to PCI, VXI to PCI, etc.), in order to assist the user in determining how data is ordered, a known floating point value of 0.12345678901234 is loaded at Power-Up in the Result Register for all channels. Channel 0 values are listed as an illustration:

| 0x3FBF | is written at address | 0xC00028 |

|--------|-----------------------|----------|

| 0x9ADD | is written at address | 0xC0002A |

| 0x3746 | is written at address | 0xC0002C |

| 0xF4C6 | is written at address | 0xC0002E |

By reading the value from these addresses, the user can identify the type of DATA(BYTE) swapping that takes place in the system and modify their code accordingly. An example of how to do the swapping is presented in Appendix A.

### **DETERMINING THE REGISTER ADDRESS**

A user wishes to set Channel 2 to the 1.0 V range. Data is to be captured linearly without the use of the low pass filter or timeout control and will trigger from the positive edge of data sent to Channel 2. To accomplish this, the user will access the Control Register for Channel 2 at register offset 0x0058. To determine the register address, this value must be added to the base address and A32 address of the module. In this example, it is assumed that the base address switches are set to 0x19, yielding a base address of 0x19000000. Since the user must write to a register, the function offset is 0x00C00000.

```

Register Address = Module Base Address + Function Offset + Register Offset

= 0x19000000 + 0x00C00000 + 0x000000058

= 0x19C00058

```

By observing the bits in the Control Register, it can be determined what data value should be sent:

The binary values are then converted into a hexadecimal format:

<u>Binary</u> <u>Hexadecimal</u> 0000 0000 0110 0010 0x0062

This determines the data value required for the aforementioned settings.

### ACCESSING THE REGISTERS

With both D16 and D32 data transfer available, the user can write either 16 or 32 bits of data to the registers. To change the settings of the module, it is only necessary to write a 16- or 32-bit integer to the specified register with the new configuration.

All registers, as defined in the following section, are 16-bit registers. A 32-bit write can be made to registers that are located in consecutive addresses. The consecutive 16-bit registers that can be accessed as 32-bit registers are:

Sample Rate Register (0x0C, 0x34, 0x5C, 0x84, 0xAC, 0xD4)

Sample Points Register (0x10, 0x38, 0x60, 0x88, 0xB0, 0xD8)

Pre-Trigger Points Register (0x14, 0x3C, 0x64, 0x8C, 0xB4, 0xDC)

Trigger Delay Register (0x18, 0x40, 0x68, 0x90, 0xB8, 0xE0)

FIFO data (0x24, 0x4C, 0x74, 0x9C, 0xC4, 0xEC)

Result Register (0x28 & 0x2C, 0x50 & 0x54, 0x78 & 0x7C, 0xA0 & 0xA4, 0xC8 & 0xCB, 0xF0 & 0xF4)

NOTE

Reading 32 bits from a 16-bit register may generate a **BERR** on the VME bus. Writing 32 bits to a 16-bit register may generate a **BERR** on the VME bus or may corrupt data in another register.

### **DESCRIPTION OF REGISTERS**

The following pages describe the registers found in the SVM2608 Register Map for A32 address space that starts at 0x00C0000. When multiple channels registers have the same functions, the offsets appear in parenthesis separated by commas with Channel 0 being listed first, followed by Channel 1, etc. For example, the description used by the Control Register Bit is applicable to all six channels at offsets 0x08 for Channel 0, 0x30 for Channel 1, 0x58 for Channel 2 and 0x80 for Channel 3, 0xA8 for Channel 4 and 0xD0 for Channel 5. This is indicated in the register description by using the following notation: (0x08, 0x30, 0x58, 0x80, 0xA8, 0xD0). Unless otherwise noted, register descriptions apply to all channels (Channels 0-5).

| Reset, Sys Fail Control, Interrupt Levels Register (0x00) — Read & Write |            |                                                                                                                                                                                                          |

|--------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D15                                                                      | Unused     | This bit is reserved for future use.                                                                                                                                                                     |

| D14                                                                      | SYSFAILCTL | System Fail Control - This bit controls whether or not the sysfail line will be masked.  0 = Card can assert sysfail line. 1 = Sysfail line is masked and card cannot assert sysfail line. Pon state = 0 |

| D13 – D3                                                                 | Unused     | These bits are reserved for future use.                                                                                                                                                                  |

|         | Reset, Sys Fail Control, Interrupt Levels Register (0x00) — Read & Write |                                                                                                                                                                                                                 |  |

|---------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         |                                                                          | Interrupt Level - These bits determine the interrupt service level.                                                                                                                                             |  |

| D2 – D0 | INTLVL2 - 0                                                              | 111 = Interrupt level 7<br>110 = Interrupt level 6<br>101 = Interrupt level 5<br>100 = Interrupt level 4<br>011 = Interrupt level 3<br>010 = Interrupt level 2<br>001 = Interrupt level 1<br>000 = No interrupt |  |

| Force Trigger, Start Register (0x02) — Read & Write |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|